# **TAS3001C** Digital Audio Processor

# Data Manual

March 2004

**DAV-Audio Products**

SLAS226B

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

# Contents

| Se | ection | Title                                                  | Page |

|----|--------|--------------------------------------------------------|------|

| 1  | Introd | uction                                                 | 1–1  |

|    | 1.1    | Description                                            | 1–1  |

|    | 1.2    | Overview                                               | 1–1  |

|    | 1.3    | Features                                               | 1–1  |

|    |        | 1.3.1 Stereo Digital Audio Processing                  | 1–1  |

|    |        | 1.3.2 Interfaces                                       | 1–2  |

|    |        | 1.3.3 Electrical and Physical                          | 1–2  |

|    | 1.4    | Applications                                           | 1–2  |

|    |        | 1.4.1 Digital Audio Controls                           | 1–2  |

|    |        | 1.4.2 Equalization                                     | 1–2  |

|    |        | 1.4.3 Loudspeaker Active Crossovers                    | 1–2  |

|    | 1.5    | Functional Block Diagram                               | 1–3  |

|    | 1.6    | Mixing/Input Scaling                                   | 1–3  |

|    | 1.7    | High-Precision, Second-Order Biquad Filter Structure   | 1–4  |

|    | 1.8    | Bass and Treble Controls                               | 1–6  |

|    | 1.9    | Soft Volume and True Soft Mute                         | 1–6  |

|    | 1.10   | Reliability and Flexibility of Digital Filtering       | 1–7  |

|    | 1.11   | Pin Assignments                                        | 1–7  |

|    | 1.12   | Pin Functions                                          | 1–8  |

|    | 1.13   | Ordering Information                                   | 1–8  |

|    | 1.14   | Power Supply                                           | 1–8  |

| 2  | Audio  | Data Formats                                           | 2–1  |

|    | 2.1    | Serial Audio Interface                                 | 2–1  |

|    |        | 2.1.1 I <sup>2</sup> S Serial Format                   | 2–2  |

|    |        | 2.1.2 Left-Justified Serial Format                     | 2–3  |

|    |        | 2.1.3 Right-Justified Serial Format                    | 2–4  |

|    | 2.2    | LRCLKOUT and SCLKOUT                                   |      |

| 3  | Serial | Control Interface (I <sup>2</sup> C)                   |      |

|    | 3.1    | I <sup>2</sup> C Protocol                              |      |

|    | 3.2    | Operation                                              | 3–2  |

|    |        | 3.2.1 Write Cycle Example                              | 3–2  |

|    |        | 3.2.2 I <sup>2</sup> C Timing and Wait Cycles          | 3–2  |

|    |        | 3.2.3 Resetting the TAS3001 I <sup>2</sup> C Interface | 3–3  |

|    |        | 3.2.4 Power-Up Conditions                              | 3–3  |

|    |        | 3.2.5 I <sup>2</sup> C Serial Port Timing              | 3–4  |

| 4  | -      | I Audio Processor                                      | 4–1  |

|    | 4.1    | Input Mixer Control                                    | 4–1  |

|   | 4.2    | Biquad B   | Block                                                      | 4–1 |

|---|--------|------------|------------------------------------------------------------|-----|

|   |        | 4.2.1      | Filter Coefficients                                        | 4–1 |

|   | 4.3    | Volume     | Control Functions                                          | 4–1 |

|   |        | 4.3.1      | Soft Volume Update                                         | 4–1 |

|   |        | 4.3.2      | Software Soft Mute                                         | 4–2 |

|   | 4.4    | Tone Co    | ontrols                                                    | 4–2 |

|   |        | 4.4.1      | Treble Control                                             | 4–2 |

|   |        | 4.4.2      | Bass Control                                               | 4–2 |

|   |        | 4.4.3      | Frequency Dependence of Treble and Bass Controls           | 4–2 |

| 5 | Device | e Operati  | ion                                                        | 5–1 |

|   | 5.1    | Device I   | nitialization                                              | 5–1 |

|   |        | 5.1.1      | Reset                                                      | 5–1 |

|   |        | 5.1.2      | Device Power On and System Reset                           | 5–1 |

|   |        | 5.1.3      | Fast Load                                                  | 5–1 |

|   | 5.2    | Power C    | Consumption                                                | 5–2 |

|   | 5.3    | Power D    | Down and Start-Up                                          | 5–2 |

| 6 | Electr | ical Char  | racteristics                                               | 6–1 |

|   | 6.1    |            | e Maximum Ratings Over Operating Free-Air                  |     |

|   |        | •          | ature Range                                                |     |

|   | 6.2    |            | nended Operating Conditions                                |     |

|   | 6.3    |            |                                                            |     |

|   | 6.4    |            | igital Specifications                                      |     |

| 7 |        |            | lio Performance for Some Typical Examples                  |     |

| 8 | -      |            | 3001 in a System                                           |     |

|   | 8.1    |            | 1 Applications                                             |     |

|   | 8.2    |            | ement-Based Speaker Correction                             |     |

|   | 8.3    |            | Based Speaker Correction                                   |     |

|   | 8.4    |            | eaker Equalization Example                                 |     |

|   | 8.5    | •          | r Correction and Equalization                              |     |

|   | 8.6    |            | S3001 Can Implement Nearly Any Second-Order IIR Filter .   |     |

| - | 8.7    |            | ing Analog Filters to Digital                              |     |

| 9 |        |            | Idspeaker Equalizer (ALE)                                  | 9–1 |

|   | 9.1    |            | tic Generation of Equalization Filters Given a Measurement | 9–1 |

|   | 9.2    |            | tic Approximation of an Equalization Curve                 | 9–1 |

|   | 9.3    |            | Filter Design                                              | 9–1 |

|   | 9.4    |            | sion of Decimal Filter Coefficients to the TAS3001 Format  | 9–1 |

|   | 9.5    | •          | of TAS3001 File Format                                     | 9–1 |

|   | 9.6    |            | es of the Filter Types Available From ALE 2.1              | 9–1 |

| _ |        |            | nd FilterMaker                                             |     |

| Α |        |            |                                                            |     |

| _ | A.1    |            | ontrol Register (MCR)                                      |     |

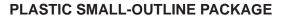

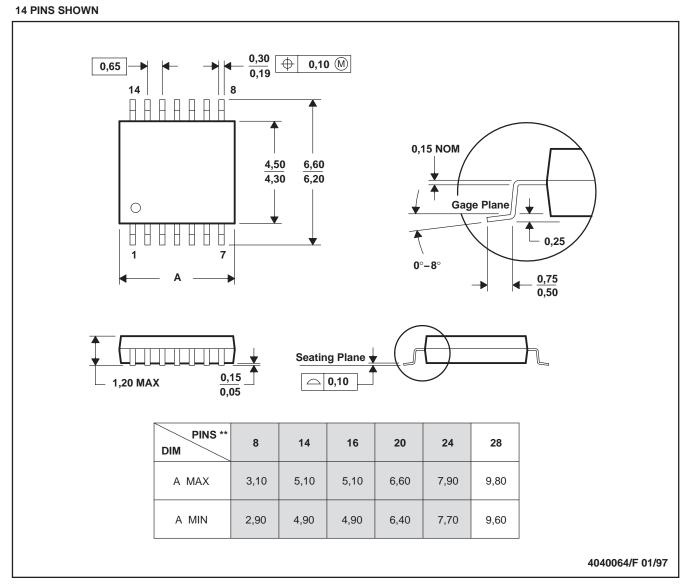

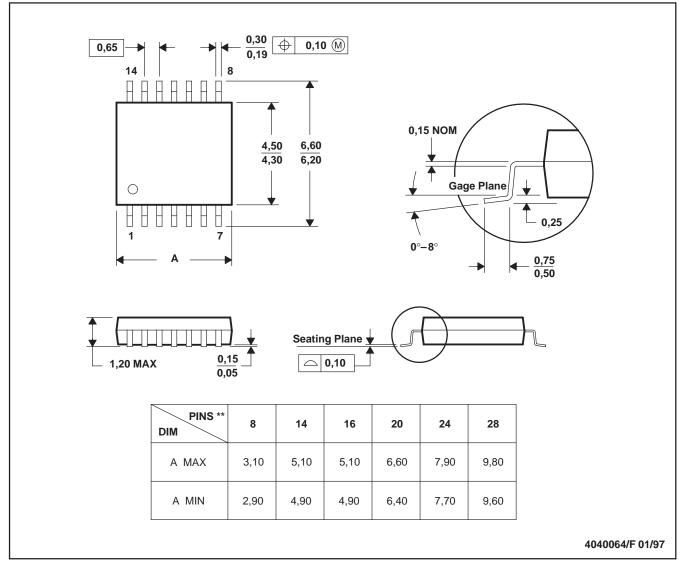

| В | Mecha  | anical Inf | ormation                                                   | B–1 |

# List of Illustrations

| Figure | Title                                                                            | Page |

|--------|----------------------------------------------------------------------------------|------|

| 1–1    | TAS3001 Signal Flow                                                              | 1–3  |

| 1–2    | Examples of High-Pass Filters                                                    | 1–4  |

| 1–3    | Examples of Equalization Filters                                                 | 1–4  |

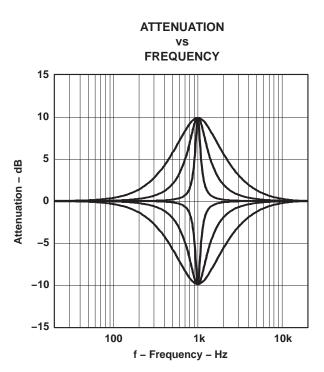

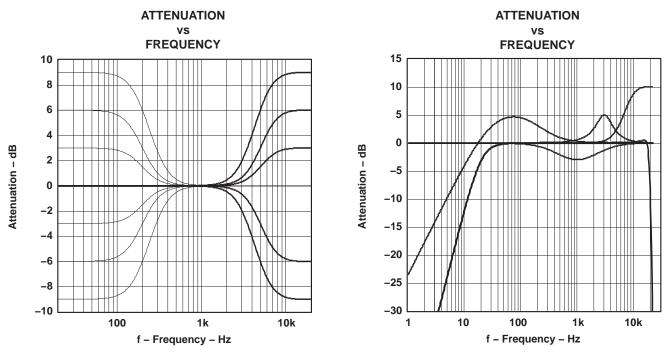

| 1–4    | Bass and Treble Shelves                                                          | 1–5  |

| 1–5    | Multiple Filter Response                                                         | 1–5  |

| 1–6    | Combed Response of the Multiple Filters                                          | 1–5  |

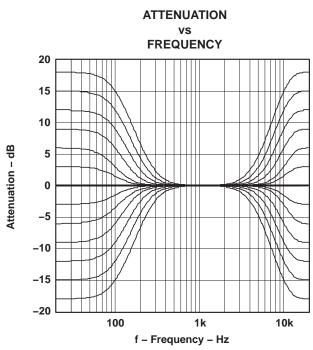

| 1–7    | Bass and Treble Filters                                                          | 1–6  |

| 1–8    | TAS3001 Pin Location Diagram                                                     | 1–7  |

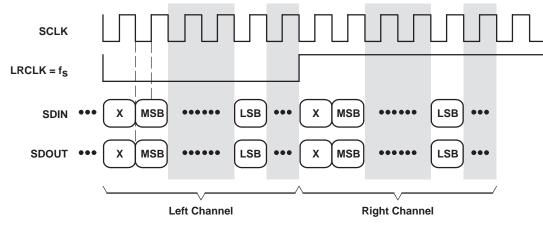

| 2–1    | I <sup>2</sup> S-Compatible Serial Format                                        | 2–2  |

| 2–2    | For Right/Left Justified, I <sup>2</sup> S, Left/Left Justified Serial Protocols | 2–3  |

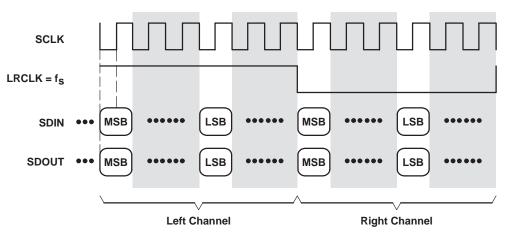

| 2–3    | Left-Justified Serial Format                                                     | 2–3  |

| 2–4    | Right-Justified Serial Format                                                    | 2–4  |

| 2–5    | Master Mode                                                                      | 2–4  |

| 2–6    | Slave Mode                                                                       | 2–5  |

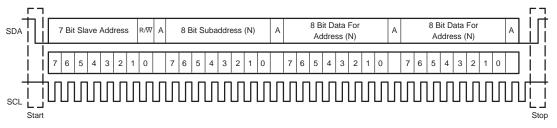

| 3–1    | Typical I <sup>2</sup> C Data Transfer Sequence                                  | 3–1  |

| 3–2    | Write Cycle Example                                                              | 3–2  |

| 3–3    | Wait Cycle Example                                                               | 3–2  |

| 3–4    | I2C Serial Port Timing                                                           | 3–4  |

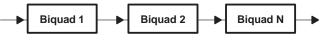

| 4–1    | Cascaded Biquad Filters                                                          | 4–1  |

| 4–2    | Audio Processing Architecture                                                    | 4–2  |

| 5–1    | Main Control Register (MCR)                                                      | 5–1  |

| 5–2    | Power-Down Timing                                                                | 5–2  |

| 5–3    | Start-Up Timing                                                                  | 5–2  |

| 6–1    | Typical TAS3001 Connection                                                       | 6–2  |

| 7–1    | Audio Performance Measurement System                                             | 7–1  |

| 7–2    | Audio Performance Test Filters                                                   | 7–2  |

| 8–1    | TAS3001 as a System Equalizer                                                    | 8–1  |

| 8–2    | TAS3001 as a Crossover and Equalizer                                             | 8–2  |

| 8–3    | Typical Small Loudspeaker Response                                               | 8–3  |

| 8–4    | Preparation for Equalization                                                     | 8–4  |

| 8–5    | After Equalization                                                               | 8–4  |

| 8–7    | Equalization Filters                                                             | 8–5  |

| 8–8    | Individual Filters                                                               | 8–6  |

# List of Illustrations (Continued)

| Combined Response             | 8–6                                                                                 |

|-------------------------------|-------------------------------------------------------------------------------------|

| Equalization Filters          | 9–2                                                                                 |

| High- and Low-Pass Filters    | 9–2                                                                                 |

| Treble and Bass Shelf Filters | 9–3                                                                                 |

| Notch Filters                 | 9–3                                                                                 |

|                               | Equalization Filters<br>High- and Low-Pass Filters<br>Treble and Bass Shelf Filters |

# List of Tables

| Table | Title                                   | Page |

|-------|-----------------------------------------|------|

| 2–1   | Serial Interface Input Options          | 2–1  |

| 2–2   | Serial Interface Output Options         | 2–1  |

| 3–1   | I <sup>2</sup> C Protocol Definitions   | 3–1  |

| 3–2   | TAS3001 I <sup>2</sup> C Address        | 3–2  |

| 3–3   | Write Cycle Example                     | 3–2  |

| 3–4   | I <sup>2</sup> C Wait States            | 3–3  |

| 4–1   | Bass Control Corner Frequencies         | 4–2  |

| 4–2   | Treble Control Corner Frequencies       | 4–2  |

| 7–1   | Audio Filter Performance                | 7–1  |

| A–1   | Register Map                            | A-1  |

| A–2   | Main Control Register (MCR)             | A-2  |

| A–3   | Main Control Register (MCR) Description | A-2  |

| A–4   | Volume Gain Values                      | A–3  |

| A–5   | Treble Control Register                 | A-4  |

| A–6   | Bass Control Register                   | A-4  |

| A–7   | Mixer1 and Mixer2 Gain Values           | A-5  |

# **1** Introduction

# 1.1 Description

The TAS3001 is a high-quality, fixed-function, 32-bit digital audio processor. This device contains a number of built-in processing functions including mixing/scaling of two digital inputs, bass and treble controls, six cascaded stereo high-precision, limit-cycle-free, second-order IIR filters, soft volume, and soft mute.

These functions can be controlled by specifying the desired operating parameters using the I<sup>2</sup>C interface.

The TAS3001 architecture preserves high-quality audio by using a 32-bit data path,  $24 \times 32$ -bit multiplies, and up to 56 bits of precision for some internal calculations. By using 24-bit filter coefficients, the TAS3001 can implement practically any second-order IIR filter with outstanding fidelity.

# 1.2 Overview

The TAS3001 is a 32-bit audio signal processor that provides mixing of two digital inputs and digital parametric equalization. In addition, this device provides high-quality, soft digital volume, bass, and treble controls. All control parameters are uploaded through the I<sup>2</sup>C port from an outside MCU.

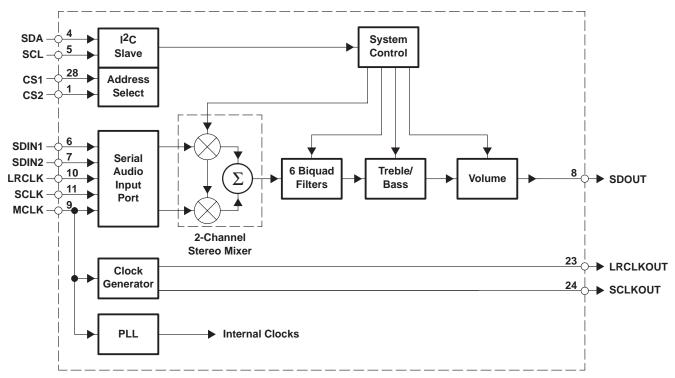

The TAS3001 has four audio processing blocks as shown in Figure 1–1.

- Two digital stereo audio inputs that can be scaled and mixed prior to processing.

- Parametric EQ that consists of six cascaded independent second-order IIR filters for each of the left and right independent channels. Each filter has five 24-bit coefficients that can be configured into many different filter functions, such as band-pass, high-pass, low-pass, shelves, notch, all-pass, high-/low-pass with shelf, etc.

- Digital bass and treble controls

- Digital soft volume and mute

The TAS3001 device uses a system clock that is generated by the internal phase-locked loop (PLL). An external master clock (MCLK) of 256 times the sampling frequency provides the reference clock for the PLL.

The TAS3001 device supports several serial data formats (I<sup>2</sup>S, left justified, right justified) with data word lengths of 16, 18, or 20. The sampling frequencies ( $f_s$ ) that are supported include 32 kHz, 44.1 kHz, 48 kHz and 96 kHz.

# 1.3 Features

#### 1.3.1 Stereo Digital Audio Processing

- Supports nine serial data formats. Receive and transmit serial data formats may be different.

- Programmable two-input digital mixer

- Programmable six-band digital parametric EQ

- Programmable digital bass and treble controls

- Programmable digital volume control with soft mute

- 108-dB dynamic range

- Sample rates from 32 kHz to 96 kHz

#### 1.3.2 Interfaces

- Two serial digital input channels

- Single serial digital output channel

- Serial I<sup>2</sup>C control channel

#### 1.3.3 Electrical and Physical

- Single 3.3-V power supply

- 28-pin PW package

- Low-power standby

### 1.4 Applications

#### 1.4.1 Digital Audio Controls

The TAS3001 can be used to provide a high-quality digital system control of volume, bass, treble, and parametric equalization.

#### 1.4.2 Equalization

The TAS3001 can be used to perform parametric equalization to correct the frequency response of loudspeakers or microphones. The TAS3001 corrects the response by applying filters to compensate for the response irregularities of the transducers.

#### 1.4.3 Loudspeaker Active Crossovers

The TAS3001 can be used to implement an active crossover for multi-way loudspeaker systems.

### 1.5 Functional Block Diagram

Figure 1–1 shows the signal flow from the inputs (SDIN1 and SDIN2) though each processing stage to the output (SDOUT) where it is passed to an external DAC, digital amplifier, or other subsequent digital data processing stage.

Each of these audio processing functions is discussed in more detail in the following sections.

#### 1.6 Mixing/Input Scaling

The TAS3001 is equipped with a dual-input stereo digital mixer. This mixer permits each input to scaled ( $-\infty$  to +18 dB) independently. A stereo sum of the scaled results is produced.

#### 1.7 High-Precision, Second-Order Biquad Filter Structure

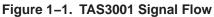

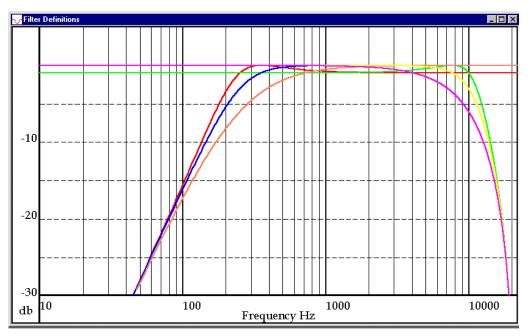

The TAS3001 has six cascaded biquad filters for the left and right channels to permit parametric equalization and filtering of the input signal. Each biquad is able to specify a wide variety of first- and second-order filter types, including high-pass, low-pass, band-pass, band-block, notch, and all-pass filter types. Examples of a few of the filters that can be implemented by the TAS3001 shapes are illustrated in Figure 1–2 though Figure 1–6.

The biquad structure is of the form:

$$H(z) = \frac{b_0 + b_1 Z^{-1} + b_2 Z^{-2}}{1 + a_1 Z^{-1} + a_2 Z^{-2}}$$

Coefficients are downloaded to the TAS3001 registers in 4.20 format.

Figure 1–3. Examples of Equalization Filters

Figure 1–5. Multiple Filter Response

The TAS3001 provides a zero-input limit-cycle-free second-order IIR filtering structure that implements a direct form I filter structure. This architecture preserves high-quality audio by using a 32-bit data path, 24 × 32-bit multiplies, and 56 bits of precision for some internal calculations. By using 24-bit filter coefficients, the TAS3001 can implement practically any second-order IIR filter with outstanding fidelity.

Texas Instruments has several tools that provide a powerful and flexible means to develop applications using the TAS3001. Chapter 8 provides examples of how the TAS3001 can be used to meet various system needs.

Figure 1–6. Combed Response of the Multiple Filters

# 1.8 Bass and Treble Controls

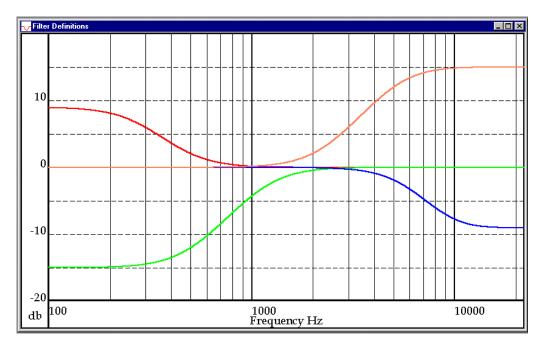

The TAS3001 has bass and treble controls that can be adjusted dynamically. These controls can be adjusted throughout their entire range of 18 dB to –18 dB without experiencing any pops, clicks, or other audible artifacts. This permits the user to have a listening experience much like what is experienced when adjusting high-quality analog controls.

Figure 1–7 shows the response for the bass and treble filters plotted at 3-dB intervals for 44.1-kHz sample-rate data.

Figure 1–7. Bass and Treble Filters

#### 1.9 Soft Volume and True Soft Mute

The TAS3001 contains a Texas Instruments proprietary soft volume update. This allows a smooth and pleasant-sounding change from one volume level to another over the entire range of volume (18 dB to mute). The volume is adjustable by downloading a 4.20 gain coefficient through the I<sup>2</sup>C interface.

Mute is implemented by loading all zeros in the volume control register. This causes the volume to ramp down over 2048 samples to a final output of zero ( $-\infty$  dB).

#### 1.10 Reliability and Flexibility of Digital Filtering

Digital filtering provides outstanding consistency, reliability, and flexibility. Once a digital filter is designed and tested in the system, it continues to perform in the same manner without change. Because digital filters are computed, their performance is exceedingly consistent and does not change due to variations in component matching, tolerances, environmental conditions, aging, or the effects of moisture and dust. Analog filters, however, are affected by all of these. The performance of analog filters can be improved, in part, by using high-quality precision components but this comes with a higher comparable cost.

One of the greatest strengths of a digital filter is its flexibility. Each filter is completely specified by five 24-bit coefficients. By modifying the value of one or more of the filter coefficients, both the filter value and filter type are changed. In a system, these modifications produce different crossover curves, different equalization curves, different sound effects (by changing the relative phase of the left and right loudspeakers) or different user graphical equalization settings.

Attempting similar changes in an analog filter would require component changes and potentially a new circuit layout. The flexibility of digital filtering provides a particular advantage to digital equalization. Because of its programmability, a single design using digital filtering can provide a wide range of filtering functions. As a result, this one design can span a number of applications.

For a product that is in production, digital filtering can permit equalization changes with minimal cost impact because of this programmability.

One concern about digital filters is that some implementations have been prone to zero-input limit cycles. This is a condition where the filter oscillates at a low level when no signal is presented. In a digital audio system, this condition may present itself as a tone or low-level noise. The TAS3001 has a patent-pending technique to combat this problem.

#### **1.11 Pin Assignments**

| P                                                                                                                                                                                             | W PACI<br>(TOP VI                                                       |                                                                                  | -                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| CS2 [<br>DV <sub>SS</sub> [<br>DV <sub>DD</sub> [<br>SDA [<br>SDIN1 [<br>SDIN2 [<br>SDOUT [<br>MCLK [<br>LRCLK [<br>SCLK [<br>AV <sub>SS</sub> _PLL [<br>AV <sub>DD</sub> _PLL [<br>CAP_PLL [ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15 | CS1<br>RESERVED<br>NC<br>SCLKOUT<br>CCLKOUT<br>RC<br>NC<br>NC<br>RESET<br>NC<br>NC<br>POWERDOWN<br>RESERVED |

NC - No internal connection

Figure 1–8. TAS3001 Pin Location Diagram

# **1.12 Pin Functions**

| TERMINAL              |                          |     |                                                                                                                              |

|-----------------------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | NO.                      | I/O | DESCRIPTION                                                                                                                  |

| AV <sub>DD</sub> _PLL | 13                       | I   | Analog power supply for the PLL                                                                                              |

| AV <sub>SS</sub> _PLL | 12                       | Ι   | Analog ground for the PLL                                                                                                    |

| CAP_PLL               | 14                       | Ι   | C1 = 1500 pF // R1 = 27 $\Omega$ + C2 = 0.068 $\mu F$ (recommended)                                                          |

| CS1                   | 28                       | Ι   | $I^{2}C$ address bit A0; low = 0, high = 1                                                                                   |

| CS2                   | 1                        | Ι   | $I^{2}C$ address bit A1; low = 0, high = 1                                                                                   |

| DVDD                  | 3                        | Ι   | Digital power supply                                                                                                         |

| DVSS                  | 2                        | Ι   | Digital ground                                                                                                               |

| LRCLK                 | 10                       | Ι   | I <sup>2</sup> S left/right clock sampling frequency (f <sub>S</sub> )                                                       |

| LRCLKOUT              | 23                       | 0   | LRCLK generated from input MCLK (usually 256 $f_S$ ) – normally routed on PCB to pin 10 (LRCLK) as input $f_S$ sample clock. |

| MCLK                  | 9                        | I   | Master clock (256 x f <sub>S</sub> )                                                                                         |

| NC                    | 17, 18, 20–22,<br>25, 26 |     | Reserved – No connection for normal operation                                                                                |

| POWERDOWN             | 16                       | I   | Powerdown input                                                                                                              |

| RESET                 | 19                       | I   | Reset, high = normal operation, low = reinitialize the device                                                                |

| RESERVED              | 15, 27                   |     | Reserved – digital ground for normal operation                                                                               |

| SCL                   | 5                        | I/O | Slave serial I <sup>2</sup> C clock                                                                                          |

| SCLK                  | 11                       | Ι   | Shift clock (bit clock)                                                                                                      |

| SCLKOUT               | 24                       | 0   | SCLK generated from input MCLK (usually 256 $f_S$ ) – normally routed on PCB to pin 11 (SCLK) as input 64 $f_S$ bit clock.   |

| SDA                   | 4                        | I/O | Slave serial I <sup>2</sup> C data                                                                                           |

| SDIN1                 | 6                        | Ι   | Serial audio data input one                                                                                                  |

| SDIN2                 | 7                        | Ι   | Serial audio data input two                                                                                                  |

| SDOUT                 | 8                        | 0   | Serial audio data output                                                                                                     |

NOTE: Reset and other control functions require MCLK to be running. The system reset operation is a synchronous operation and requires a minimum of four MCLK cycles to reset the device.

# **1.13 Ordering Information**

| т <sub>А</sub> | PACKAGE            |  |  |

|----------------|--------------------|--|--|

| I A I          | SMALL OUTLINE (PW) |  |  |

| 0°C to 70°C    | TAS3001CPW         |  |  |

# 1.14 Power Supply

- Digital supply voltage—DV<sub>DD</sub>, DV<sub>SS</sub> of 3.3 V

- Analog supply voltage—AV<sub>DD</sub>\_PLL, AV<sub>SS</sub>\_PLL of 3.3 V

NOTE: AV<sub>DD</sub> and AV<sub>SS</sub> for the PLL are derived from the digital supply and digital ground.

# 2 Audio Data Formats

#### 2.1 Serial Audio Interface

The TAS3001 operates in digital audio slave mode only. The TAS3001 supports three serial audio data formats: I<sup>2</sup>S, left-justified, and right-justified. Data word lengths of 16, 18, and 20 bits are supported.

Data is input into SDIN1 and SDIN2 under the influence of the master clock (MCLK), left/right clock (LRCLK), and shift clock (SCLK) inputs.

Data is output on the SDOUT pin under the influence of the master clock (MCLK) input plus the left/right clock (LRCLKOUT) and shift clock (SCLKOUT) outputs. LRCLKOUT and SCLKOUT are generated from the MCLK input (usually at  $256 \times f_s$ ). Typically these are routed on the PCB to LRCLK (as the input  $f_s$  sample clock) and SCLK (as the input  $64 \times f_s$  bit clock).

The TAS3001 device is compatible with 10 different serial interfaces. Available interface options are I<sup>2</sup>S, right-justified, and left-justified. Table 2–1 and Table 2–2 indicate how the 10 options are selected using the I<sup>2</sup>C bus and the main control register (MCR, I<sup>2</sup>C address 01h). All serial interface options at either 16, 18, or 20 bits operate with SCLK at  $64 \times f_s$ . The 16-bit mode, left-justified, can operate at  $32 \times f_s$  or  $64 \times f_s$ .

| MODE | MCR BIT 6<br>SC | MCR BITS 3–2<br>F(1,0) | MCR BITS 1–0<br>W(1,0) | SERIAL INTERFACE<br>SDIN1, SDIN2                     |  |  |

|------|-----------------|------------------------|------------------------|------------------------------------------------------|--|--|

| 0    | 0               | 00                     | 00                     | 16-bit, left-justified, $32 \times f_S$              |  |  |

| 1    | 1               | 00                     | 00                     | 16-bit, left-justified, $64 \times f_S$              |  |  |

| 2    | 1               | 01                     | 00                     | 16-bit, right-justified, $64 \times f_S$             |  |  |

| 3    | 1               | 10                     | 00                     | 16-bit, I <sup>2</sup> S, $64 \times f_S$            |  |  |

| 4    | 1               | 00                     | 01                     | 18-bit, left-justified, $64 \times f_S$              |  |  |

| 5    | 1               | 01                     | 01                     | 18-bit, right-justified, $64 \times f_S$             |  |  |

| 6    | 1               | 10                     | 01                     | 18-bit, I <sup>2</sup> S, $64 \times f_S$            |  |  |

| 7    | 1               | 00                     | 10                     | 20-bit, left-justified, $64 \times f_S$              |  |  |

| 8    | 1               | 01                     | 10                     | 20-bit, right-justified, $64 \times f_S$             |  |  |

| 9    | 1               | 10                     | 10                     | 20-bit, I <sup>2</sup> S, 64 $\times$ f <sub>S</sub> |  |  |

Table 2–1. Serial Interface Input Options

Table 2–2.

Serial Interface Output Options

| -    |                 |                        |                        |                                                      |  |

|------|-----------------|------------------------|------------------------|------------------------------------------------------|--|

| MODE | MCR BIT 6<br>SC | MCR BITS 5–4<br>E(1,0) | MCR BITS 1–0<br>W(1,0) | SERIAL INTERFACE<br>SDOUT                            |  |

| 0    | 0               | 00                     | 00                     | 16-bit, left-justified, $32 \times f_S$              |  |

| 1    | 1               | 00                     | 00                     | 16-bit, left-justified, $64 \times f_S$              |  |

| 2    | 1               | 01                     | 00                     | 16-bit, right-justified, $64 \times f_S$             |  |

| 3    | 1               | 10                     | 00                     | 16-bit, I <sup>2</sup> S, $64 \times f_S$            |  |

| 4    | 1               | 00                     | 01                     | 18-bit, left-justified, $64 \times f_S$              |  |

| 5    | 1               | 01                     | 01                     | 18-bit, right-justified, $64 \times f_S$             |  |

| 6    | 1               | 10                     | 01                     | 18-bit, I <sup>2</sup> S, $64 \times f_S$            |  |

| 7    | 1               | 00                     | 10                     | 20-bit, left-justified, $64 \times f_S$              |  |

| 8    | 1               | 01                     | 10                     | 20-bit, right-justified, $64 \times f_S$             |  |

| 9    | 1               | 10                     | 10                     | 20-bit, I <sup>2</sup> S, 64 $\times$ f <sub>S</sub> |  |

Figure 2–1 through Figure 2–4 illustrate the relationship between the SCLK, LRCLK, and the serial data input and output protocol options.

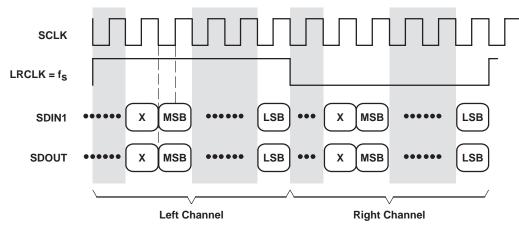

### 2.1.1 I<sup>2</sup>S Serial Format

The following are characteristics of this protocol:

- LRCLK is the left/right clock. The left channel is transmitted when LRCLK is low. The right channel is transmitted when LRCLK is high.

- SDIN is sampled with the rising edge of SCLK.

- SDOUT is transmitted on the falling edge of SCLK.

- LRCK must have a 50% duty cycle.

Figure 2–1. I<sup>2</sup>S-Compatible Serial Format

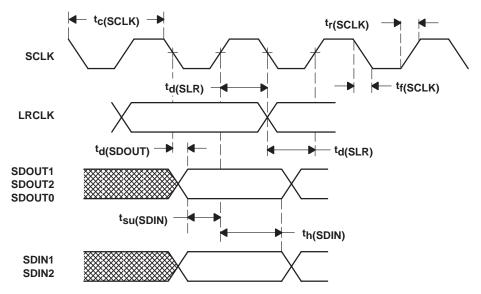

# 2.1.1.1 I<sup>2</sup>S Signal Timing

|                       | PARAMETER                                  | MIN | TYP     | MAX                         | UNIT |

|-----------------------|--------------------------------------------|-----|---------|-----------------------------|------|

| <sup>t</sup> c(SCLK)  | SCLK frequency                             |     |         | 6.144                       | MHz  |

| <sup>t</sup> d(SLR)   | SCLK rising to LRCLK edge                  | 20  |         |                             | ns   |

| <sup>t</sup> d(SDOUT) | SDOUT valid from SCLK falling (see Note 1) |     |         | $1/(256 \times f_{S}) + 10$ | ns   |

| <sup>t</sup> su(SDIN) | SDIN setup before SCLK rising edge         | 20  |         |                             | ns   |

| <sup>t</sup> h(SDIN)  | SDIN hold after SCLK rising edge           | 100 |         |                             | ns   |

| · ·                   | LRCLK                                      | 32  | 44.1/48 | 96                          | kHz  |

|                       | Duty cycle                                 |     | 50%     |                             |      |

NOTE 1: Maximum of 50-pF external load on SDOUT.

Figure 2–2. For Right/Left Justified, I<sup>2</sup>S, Left/Left Justified Serial Protocols

#### 2.1.2 Left-Justified Serial Format

The following are characteristics of this protocol:

- LRCLK is the left/right clock. The left channel is transmitted when LRCLK is high. The right channel is transmitted when LRCLK is low.

- The SDIN data is justified to the leading edge of LRCLK.

- The MSBs are transmitted at the same time as the LRCLK edge and captured at the very next rising edge of SCLK.

- Serial data is sampled into the device on the rising edge of SCLK.

- Serial data is transmitted out of the device on the falling edge of SCLK.

- SCLK =  $32 \times LRCLK$  ( $32 \times f_s$  SCLK is only supported for 16-bit data) or  $64 \times LRCLK$

- In this mode, LRCLK does not have to be a 50% duty-cycle clock. The number of bits used in the interface sets the minimum duty cycle. There must be enough SCLK pulses to shift all of the data.

Figure 2–3. Left-Justified Serial Format

#### 2.1.3 Right-Justified Serial Format

The following are characteristics of this protocol:

- LRCLK is the left/right clock. The left channel is transmitted when LRCLK is high. The right channel is transmitted when LRCLK is low.

- The SDIN data (recorded data) is justified to the trailing edge of the LRCLK.

- Serial data is sampled on the rising edge of SCLK.

- Serial data is transmitted on the falling edge of SCLK.

- In this mode, LRCLK does not have to be a 50% duty-cycle clock. The number of bits used in the interface sets the minimum duty cycle. There must be enough SCLK pulses to shift all of the data.

Figure 2–4. Right-Justified Serial Format

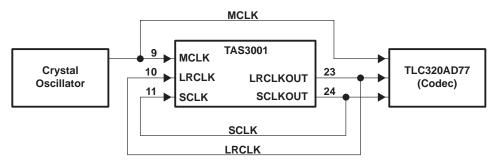

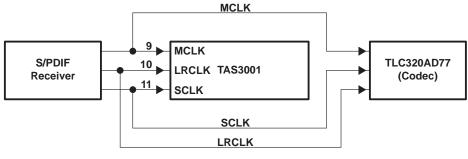

# 2.2 LRCLKOUT and SCLKOUT

The digital audio processor and on-chip logic are sequenced using an internal system clock that is derived from MCLK (master clock). Also derived from MCLK are the LRCLKOUT and SCLKOUT signals that provide clocks to the TAS3001 and other devices in the system.

The TAS3001 allows multiple system clocking schemes. In Figure 2–5, the TAS3001 provides system clocks (LRCLK and SCLK) to other parts of the system. In Figure 2–6, a system master other than the TAS3001, provides system clocks (LRCLK and SCLK) to the TAS3001.

Figure 2–5. Master Mode

# **3** Serial Control Interface (I<sup>2</sup>C)

The TAS3001 operation is controlled using the RESET signal and the serial control interface. Control information is downloaded into the TAS3001 control registers by an I<sup>2</sup>C master device, such as a microprocessor, microcontroller, or DSP. These registers control the settings for volume, bass, treble, mixing, and filtering. A description of the register addresses and control formats is given in Appendix A.

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Each device is addressed by sending a unique 7-bit slave address plus an R/W bit (1 byte).

All I<sup>2</sup>C compatible devices are controlled using the SDA and SCL signals using a wire-ANDed connection. A pullup resistor must be used to set the high level on the bus. The TAS3001 operates in standard I<sup>2</sup>C mode up to 100 kbps with as many devices on the bus as desired up to the capacitance load limit of 400 pF.

The TAS3001 is an I<sup>2</sup>C slave-only device; therefore, at least one device connected to the I<sup>2</sup>C bus with this device must operate in master mode. The pullup resistor is generally 4.99 k $\Omega$ . Upon power up, the I<sup>2</sup>C is in an unknown state until the master clock has been applied and the TAS3001 has been reset. Prior to reset, the TAS3001 may hold the SDA and/or SCL lines low. This creates I<sup>2</sup>C communication errors for any other device that attempts to use the bus.

# 3.1 I<sup>2</sup>C Protocol

The bus standard uses transitions on the data pin (SDA) while the clock is high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 3–1. These start and stop conditions for the I<sup>2</sup>C bus are required by standard protocol to be generated by the master. The master must also generate the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then wait for an acknowledge condition. The slave holds SDA low during acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence.

After each 8-bit word, an acknowledgment must be transmitted by the receiving device. There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 3–1. Definitions for the I<sup>2</sup>C protocol terms are listed in Table 3–1.

Figure 3–1. Typical I<sup>2</sup>C Data Transfer Sequence

| DEFINITION | DESCRIPTION                                                                                |

|------------|--------------------------------------------------------------------------------------------|

| Master     | The device that initiates a transfer, generates clock signals, and terminates the transfer |

| Receiver   | The device that receives data                                                              |

| Slave      | The device addressed by the master                                                         |

Table 3–1. I<sup>2</sup>C Protocol Definitions

# 3.2 Operation

To permit multiple devices to be controlled via the I<sup>2</sup>C bus, each slave device has an address. The TAS3001 has been assigned four unique addresses to permit multiple TAS3001s to be used in a system. The addresses are selected using the CS1 and CS2 pins. These four addresses, listed in Table 3–2, are licensed I<sup>2</sup>C addresses and do not conflict with other licensed I<sup>2</sup>C audio devices. To communicate with the TAS3001, the I<sup>2</sup>C master must use the address 01101XX. In addition to the 7-bit device address, subaddresses are used to direct communication to the proper memory location within the device. A complete table of subaddresses and control registers is provided in Appendix A, *Software Interface*.

| I <sup>2</sup> C ADDRESS BYTE | A6-A2 | CS2(A1) | CS1(A0) | R/W |

|-------------------------------|-------|---------|---------|-----|

| 68h                           | 01101 | 0       | 0       | 0   |

| 6Ah                           | 01101 | 0       | 1       | 0   |

| 6Ch                           | 01101 | 1       | 0       | 0   |

| 6Eh                           | 01101 | 1       | 1       | 0   |

Table 3–2. TAS3001 I<sup>2</sup>C Address

#### 3.2.1 Write Cycle Example

An example write cycle is demonstrated in Figure 3–2 and Table 3–3.

#### Figure 3–2. Write Cycle Example

| Tab           | e 5-5. While Cycle Example                             |

|---------------|--------------------------------------------------------|

| FUNCTION      | DESCRIPTION                                            |

| Start         | Start condition as defined in I <sup>2</sup> C         |

| Slave address | 0110100 (CS1 = CS2 = 0)                                |

| R/W           | 0 (write)                                              |

| A             | Acknowledgement as defined in I <sup>2</sup> C (slave) |

| Subaddress    | 00000110 (see Appendix A, Software Interface)          |

| Data          | 00011100 (see Appendix A, Software Interface)          |

| Stop          | Stop condition as defined in I <sup>2</sup> C          |

#### Table 3–3. Write Cycle Example

Whenever writing to a subaddress, the correct number of data bytes must follow in order to complete the write cycle. For example, if the volume control register with subaddress 04h is written to, six bytes of data must follow; otherwise, the cycle will be incomplete and errors will occur.

#### 3.2.2 I<sup>2</sup>C Timing and Wait Cycles

The TAS3001 issues I<sup>2</sup>C wait cycles to regulate the flow of command information. The TAS3001 can issue wait cycles for each instruction. For any instruction, the TAS3001 can issue up to a one sample (23  $\mu$ s) wait between data bytes and between the last data byte and the I<sup>2</sup>C stop. This wait is generated after the acknowledgement. The duration of this wait cycle is slightly longer than a sample interval, on the order of 1.1 x 1 ÷ F<sub>s</sub> ( or 25  $\mu$ s at 44.1 kHz). This wait cycle is illustrated in Figure 3–3.

| Start | Slave Address | R/W | Α | Subaddress | Α | Data Byte 1 | А | Wait | Data Byte 1 | А | Wait | Data Byte 2 | А | Wait | Data Byte N | А | Wait | Stop |

|-------|---------------|-----|---|------------|---|-------------|---|------|-------------|---|------|-------------|---|------|-------------|---|------|------|

|-------|---------------|-----|---|------------|---|-------------|---|------|-------------|---|------|-------------|---|------|-------------|---|------|------|

#### Figure 3–3. Wait Cycle Example

The TAS3001 can also issue an  $I^2C$  wait state after receiving an entire volume or tone command. The TAS3001 produces these wait cycles while it executes the interpolation algorithms from the present setting to the new setting. The volume command always takes the same amount of time to process for a given sample rate. The treble and bass commands vary depending upon the current index and the destination index. E.g., moving from -18 dB to 18 dB or vice versa produces the longest wait.

However, this wait cycle does not occur during the volume or tone change command, instead it occurs during the next command after the acknowledgement of the first data byte.

Table 3–4 gives typical values of the wait states of the TAS3001 commands.

|              | SYSTE  | M SAMPLIN |        |        |                                               |

|--------------|--------|-----------|--------|--------|-----------------------------------------------|

|              | 32 kHz | 44.1 kHz  | 48 kHz | 96 kHz | COMMENT                                       |

| Volume       | 62 ms  | 49 ms     | 41 ms  | 21 ms  | Not dependent on size of change               |

| Bass         | 231 ms | 167 ms    | 153 ms | 77 ms  | 18 dB to –18 dB (proportional to step change) |

| Treble       | 231 ms | 167 ms    | 153 ms | 77 ms  | 18 dB to –18 dB (proportional to step change) |

| Mixer        | None   | None      | None   | None   |                                               |

| Equalization | None   | None      | None   | None   |                                               |

Table 3–4. I<sup>2</sup>C Wait States

The I<sup>2</sup>C operation sequence that the TAS3001 uses to assert an I<sup>2</sup>C wait cycle is:

- 1. The TAS3001 detects a valid start condition and correct device ID. At this point the TAS3001 issues an ACK.

- 2. The TAS3001 decodes the eight-bit subaddress and issues another ACK.

- 3. The TAS3001 decodes the first data byte and issues a third ACK.

- 4. At this point, the TAS3001 device can hold the SCL clock line low until the internal controller is ready to accept more data. This is an I<sup>2</sup>C slave wait state.

There are two ways a master can handle the I<sup>2</sup>C slave wait.

- The preferred way to handle wait states is to use an I<sup>2</sup>C master that recognizes wait states. During the

wait-state period, the master stops sending data over I<sup>2</sup>C. In this case, when the master releases the clock

to go high after a slave ACK (to latch in the next bit of data), the master monitors the SCL line and ensures

that the slave has released SCL. Once SCL has been released the master can start the next transmission.

- Alternatively, if this function is not available on the system controller, fixed delays can be implemented in the system software to ensure that the TAS3001 is ready to receive additional data. Sending I<sup>2</sup>C data while the TAS3002 device is busy causes errors and the device locks up and have to be reset.

Issuing a stop command in the middle of an I<sup>2</sup>C transaction puts the TAS3001 I<sup>2</sup>C slave block into an unknown state, possibly locking up the controller or causing it to send incorrect data to the signal processing block.

#### 3.2.3 Resetting the TAS3001 I<sup>2</sup>C Interface

To put the TAS3001 back into a known state, an I<sup>2</sup>C transaction with a subaddress of 00h and followed by 16 bytes of zeros clears out the I<sup>2</sup>C slave block buffer. Resetting the device also puts it into a known state.

During normal operation, the TAS3001 should never issue a NACK. If the TAS3001 issues a NACK, this is an indication of an I<sup>2</sup>C protocol discrepancy.

#### 3.2.4 Power-Up Conditions

Upon system power up, the I<sup>2</sup>C bus SCL can initialize in a mode in which the line is held low. This prevents any I<sup>2</sup>C operations from being performed. To prevent this from occurring, always hold RESET low for a minimum of 10 MCLK clock cycles after applying power.

Upon reset, the TAS3001 goes through an initialization sequence with a duration of 5 ms.

Before a reset, the SDA and SCL lines may be held low by the device.

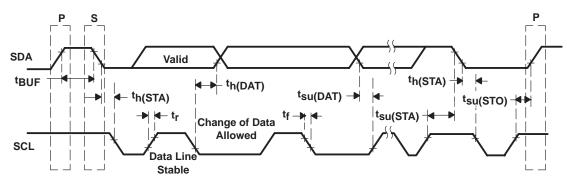

# 3.2.5 I<sup>2</sup>C Serial Port Timing

|                      | PARAMETER                                   | MIN | MAX  | UNIT |

|----------------------|---------------------------------------------|-----|------|------|

| f(scl)               | SCL clock frequency                         | 0   | 100  | kHz  |

| <sup>t</sup> BUF     | Bus free time between start and stop        | 4.7 |      | μs   |

| <sup>t</sup> w(low)  | Pulse duration, SCL clock low (see Note 1)  | 4.7 |      | μs   |

| <sup>t</sup> w(high) | Pulse duration, SCL clock high (see Note 2) | 4   |      | μs   |

| <sup>t</sup> h(STA)  | Hold time, repeated start                   | 4   |      | μs   |

| <sup>t</sup> su(STA) | Setup time, repeated start                  | 4.7 | 20   | μs   |

| <sup>t</sup> h(DAT)  | Hold time, data                             | 0†  |      | μs   |

| <sup>t</sup> su(DAT) | Setup time, data                            | 250 |      | ns   |

| t <sub>r</sub>       | Rise time for SDA and SCL                   |     | 1000 | ns   |

| tf                   | Fall time for SDA and SCL                   |     | 300  | ns   |

| <sup>t</sup> su(STO) | Setup time for stop condition               | 4   |      | μs   |

<sup>†</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL. NOTES: 1.  $t_{W(low)}$  is measured from the end of  $t_{f}$  to the beginning of  $t_{r.}$ 2.  $t_{W(high)}$  is measured from the end of  $t_{f}$  to the beginning of  $t_{f.}$

Figure 3–4. I<sup>2</sup>C Serial Port Timing

# 4 Digital Audio Processor

#### 4.1 Input Mixer Control

The TAS3001 is capable of mixing two channels of serial audio data. The mixer permits each input to scaled ( $-\infty$  to +18 dB) independently and then a stereo summation is performed. One important function of this circuit is to scale the input signals down to compensate for gains in the equalization settings and the bass and treble controls. This prevents the system from exceeding the maximum digital signal output.

The mixer operation is controlled by loading values into the MIXER1 (07h) and MIXER2 (08h) control registers. The mixer control values are in 4.20 format—4 bits for the integer and 20 bits for the fraction. The formula for converting a 4.N number to dB is:  $dB = 20 \log(X)$ , where X is a positive 4.N number. To mute a mixer channel, 0s are loaded into its respective mixer control register.

In order to transmit mixer control values over  $I^2C$ , it is necessary to separate each value into three bytes. The first nibble of byte 2 is the integer; the second nibble of byte 2 and bytes 1 and 0 are the fraction.

Table A–7 contains dB converted into 4.20 numbers for the range –70 dB to 18 dB, although any positive 4.20 number can be used.

The mixer operation is updated instantly in response to a control register change. This may cause audible artifacts when changing mixer settings outside of fast load mode.

# 4.2 Biquad Block

The biquad block consists of six digital biquad filters per channel organized in a cascade structure as shown in Figure 4–1. Each of these biquad filters has five downloadable 24-bit (4.20) coefficients. Each stereo channel has independent coefficients.

Figure 4–1. Cascaded Biquad Filters

#### 4.2.1 Filter Coefficients

The filter coefficients for the TAS3001 are downloaded through the I<sup>2</sup>C port and loaded into the biquad memory space. Digital audio data coming into the device is processed by the biquad filters and then output from the device, usually to an external DAC. Any biquad filter may be downloaded and processed by the TAS3001. The biquad structure that is used for the parametric equalization filters is:

$$H(z) = \frac{b_0 + b_1 Z^{-1} + b_2 Z^{-2}}{1 + a_1 Z^{-1} + a_2 Z^{-2}}$$

The coefficients for these filters are quantized and represented in 4.20 format—4 bits for the integer part and 20 bits for the fractional part. Each biquad uses five coefficients to define the operation.

# 4.3 Volume Control Functions

#### 4.3.1 Soft Volume Update

The TAS3001 implements a Texas Instruments proprietary soft volume update. This update allows a smooth and pleasant-sounding change from one volume level to another over the entire range of volume (18 dB to mute).

The volume is adjustable by downloading a 4.20 gain coefficient through the  $I^2C$  interface to register (04h). Table A–4 in the Appendix lists the 4.20 coefficient values for 0.5-dB volume steps for the range of –70 dB to 18 dB. However, positive 4.20 values other than those listed in Table A–4 are allowed.

Right and left channel volumes can be unganged and set to different values to implement balance control.

#### 4.3.2 Software Soft Mute

Mute is implemented by loading all zeros in the volume control register. This causes the volume to ramp down automatically over a maximum of 2048 samples to a final output of zero ( $-\infty$  dB).

#### 4.4 Tone Controls

#### 4.4.1 Treble Control

The treble gain level may be adjusted within the range of 18 dB to -18 dB with 0.5 dB step resolution. The level changes are accomplished by downloading the one byte treble control codes into the treble control register (05h). The bass control codes are shown in Table A-5.

#### 4.4.2 Bass Control

The bass gain level may be adjusted within the range of 18 dB to -18 dB with 0.5 dB step resolution. The level changes are accomplished by downloading the one byte bass control codes into the bass control register (06h). The treble control codes are shown in Table A-6.

#### 4.4.3 Frequency Dependence of Treble and Bass Controls

The bass and treble controls are based upon fixed filter coefficients. The coefficients define a response that is a based upon the data sample rate. As a result, if the sample rate is increased or decreased by a factor, the filter frequency response will increase or decrease in frequency by an equal factor. Table 4–1 and Table 4–2 show the relationship between the sample frequency and corner frequency for the bass and treble controls.

|                  | 33 0011101 |        | quenoies |        |

|------------------|------------|--------|----------|--------|

| Sampling Rate    | 32,000     | 44,100 | 48,000   | 96,000 |

| Corner Frequency | 72.6       | 100.0  | 108.8    | 217.7  |

Table 4–1. Bass Control Corner Frequencies

Table 4–2.

Treble Control Corner Frequencies

| Sampling Rate    | 32,000 | 44,100 | 48,000 | 96,000 |

|------------------|--------|--------|--------|--------|

| Corner Frequency | 7,256  | 10,000 | 10,884 | 21,769 |

# **5** Device Operation

# 5.1 Device Initialization

#### 5.1.1 Reset

The reset pin allows the device to be reset. The reset operation is a synchronous operation requiring MCLK to perform the sequence of reset operations. During reset, the TAS3001 returns to the default state as described in this section and goes through the initialization process. The TAS3001 does not reset automatically when power is applied to the device.

A reset is required after power is applied to any of the power pins.

Required conditions for a successful reset:

- MCLK is running.

- RESET is low for a minimum of 10 MCLK cycles.

The reset operation typically takes 5 ms to complete.

Once reset has completed, the master control register (MCR) should be set. The MCR sets the serial mode and fast load. It is recommended that the MCR be set only once, following reset.

#### 5.1.2 Device Power On and System Reset

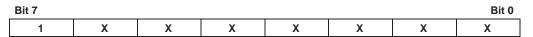

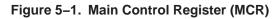

When power is applied to the TAS3001, the device powers up in an unknown state. It must be reset before the device will be in a known state. It is recommended that RESET be applied following power up. The TAS3001 performs its internal reset operations in 5 ms and is then ready for operation. Following the reset, the TAS3001 initializes to its default state (fast load mode). The main control register is configured to 1XXX XXXX, where X is not initialized, as shown in Figure 5–1 (see Appendix A for a complete description of the MCR). Only the fast load bit set to a 1 in the main control register. This puts the device into fast load mode (see the *Initialization* section). All random access memory (RAM) will be initialized (previous data will be overwritten).

The I<sup>2</sup>C address pins (CS1 and CS2) should be driven or biased to set the TAS3001 to a known I<sup>2</sup>C address. This also ensures the I<sup>2</sup>C port is active immediately after the reset initialization phase. Furthermore, when implementing a three- or six-speaker system, the CS1 and CS2 pins must always be driven or set to unique addresses on all devices. The I<sup>2</sup>C port is powered up but does not acknowledge any I<sup>2</sup>C bus activity until the entire device has been initialized. This initialization typically takes 5 ms.

#### 5.1.3 Initialization

After reset, the system enters fast-load mode and the following occur as part of initialization:

- All of the parametric EQ is initialized to 0 dB (all-pass).

- The tone (bass/treble) is set to 0 dB.

- The mix function sets SDIN1 to 0 dB and SDIN2 to mute (no-pass).

- The volume is set to mute.

While in fast-load mode, it is possible to update the parametric EQ without any audio processing delay. The audio processor pauses while the RAM is being updated in this mode. It is recommended that parametric EQ be downloaded in this mode. Bass and treble cannot be downloaded in this mode. Mixer1 and Mixer2 registers can be downloaded in this mode or normal mode (FL bit = 0). It is not recommended to download the volume control register and mixer registers in this mode. Once the download is complete, the fast-load bit needs to be cleared by writing a 0 into bit 7 of the main control register. This puts the TAS3001 into normal mode.

**NOTE:** While in the fast-load mode, the TAS3001 does not accept audio. The device must be set to the normal mode before it can accept and process audio data.

When coming out of fast-load mode, it is good practice to be sure that the system is muted. This prevents the system from producing spurious pops and clicks. Once back in normal mode, treble, bass, and volume controls can be downloaded to complete device setup.

#### 5.2 Power Consumption

During normal operation the average power consumption is 20 mA.

When RESET is held low, asserted, the TAS3001 draws an average current of 35 mA.

#### 5.3 Power Down and Restart

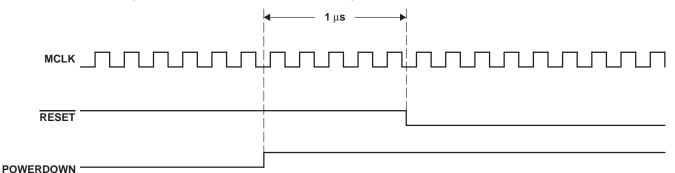

The TAS3001 can be placed in a low-power mode. It is entered synchronously by asserting the POWERDOWN pin high, logic 1, followed by asserting the  $\overrightarrow{\text{RESET}}$  pin low, logic 1, 1 µs later. Figure 5–2 illustrates the timing for power down. MCLK must be present for the TAS3001 to enter the power-down mode.

NOTE: RESET and POWERDOWN do not have to be synchronized with MCLK.

#### Figure 5–2. Power-Down Timing

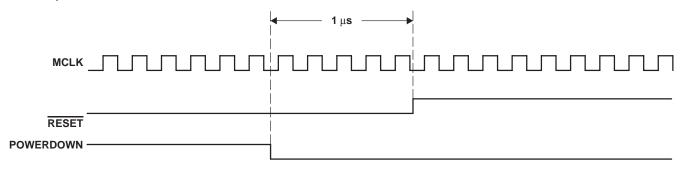

To recover from the power-down state, the POWERDOWN pin is set low, logic 0, followed by asserting the  $\overline{\text{RESET}}$  pin high, logic 0, 1 µs later. Figure 5–3 illustrates the timing for start-up. MCLK must be present for the TAS3001 to exit the power-down mode.

NOTE: RESET and POWERDOWN do not have to be synchronized with MCLK.

Figure 5–3. Start-Up Timing

# **6** Electrical Characteristics

# 6.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (Unless Otherwise Noted)<sup>†</sup>

| Supply voltage range, AV <sub>DD</sub> _PLL, DV <sub>DD</sub> –0.3 V to 4. | .2 V |

|----------------------------------------------------------------------------|------|

| Digital input voltage range                                                | .3 V |

| Operating free-air temperature range, T <sub>A</sub> 0°C to 70             | 0°C  |

| Storage temperature range, T <sub>stg</sub>                                | 0°C  |

| Case temperature for 10 seconds, T <sub>C</sub> 122.3                      | 3°C  |

| Lead temperature from case for 10 seconds                                  | 8°C  |

| ESD tolerance <sup>‡</sup> 200                                             | 0 V  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> Human body model per method 3015.2 of MIL-STD-883B.

#### 6.2 Recommended Operating Conditions

|                                                      | MIN | NOM | MAX | UNIT |

|------------------------------------------------------|-----|-----|-----|------|

| PLL supply voltage, AV <sub>DD</sub>                 | 3   | 3.3 | 3.6 | V    |

| Digital IC supply voltage, DV <sub>DD</sub>          | 3   | 3.3 | 3.6 | V    |

| Capacitive load for each bus line CL(bus) (SDA, SCL) |     |     | 400 | pF   |

| Operating free-air temperature, T <sub>A</sub>       | 0   | 25  | 70  | °C   |

#### 6.3 Power Consumption

| PARAMETER                              | TEST CONDITIONS                                | 32–48 kHz<br>SAMPLE<br>RATE | 96 kHz<br>SAMPLE<br>RATE | UNIT |

|----------------------------------------|------------------------------------------------|-----------------------------|--------------------------|------|

|                                        |                                                | TYP                         | TYP                      |      |

|                                        | $V_{DD} = 3.3 V$ , No load                     | 20                          | 40                       |      |

| PLL and digital IC supply current, IDD | V <sub>DD</sub> = 3.3 V, No load, Reset active | 35                          | 70                       | mA   |

|                                        | V <sub>DD</sub> = 3.3 V, No load, Standby      | 2                           | 4                        |      |

#### 6.4 Static Digital Specifications

|                    | PARAMETER                         | TEST CONDITIONS         | MIN  | TYP MAX              | UNIT |

|--------------------|-----------------------------------|-------------------------|------|----------------------|------|

| $V_{\text{IH}}$    | High-level input voltage          |                         | 2    | V <sub>DD</sub> +0.3 | V    |

| $V_{IL}$           | Low-level input voltage           |                         | -0.3 | 0.8                  | V    |

| VOH                | High-level output voltage         | $I_{O} = -1 \text{ mA}$ | 2.4  | V <sub>DD</sub>      | V    |

| VOL                | Low-level output voltage          | $I_{O} = 4 \text{ mA}$  |      | 0.4                  | V    |

| IIН                | High-level input leakage current  |                         | -10  | 10                   | μΑ   |

| ۱ <sub>IL</sub>    | Low-level input leakage current   |                         | -10  | 10                   | μΑ   |

| I <sub>OZ(H)</sub> | High-level output leakage current | SCL, SDA                | -10  | 10                   | μΑ   |

| I <sub>OZ(L)</sub> | Low-level output leakage current  | SCL, SDA                | -10  | 10                   | μΑ   |

# 7 Measured Audio Performance for Some Typical Examples

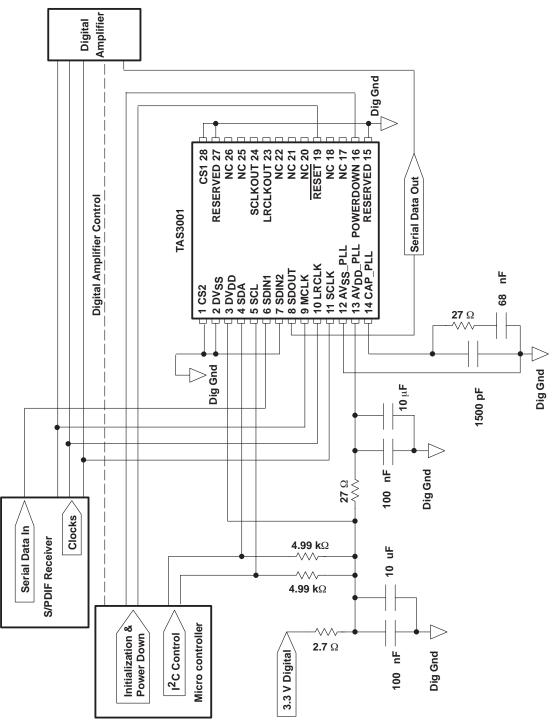

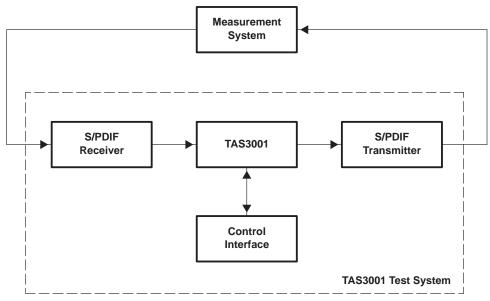

To illustrate the performance of the TAS3001, a series of measurements was performed on a system shown in Figure 7–1.

Figure 7–1. Audio Performance Measurement System

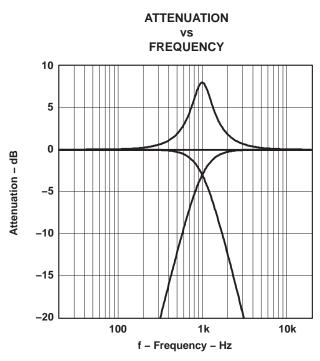

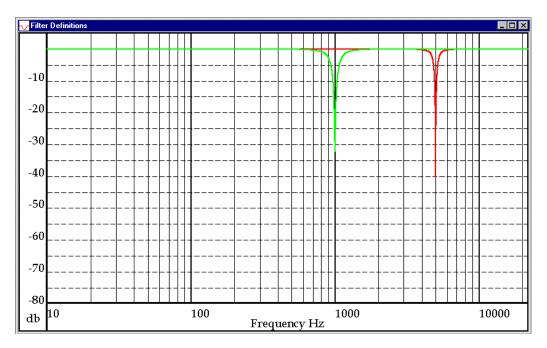

The system performance was measured for three filter types at 48 kHz.

- Butterworth high-pass filter at 1 kHz

- Butterworth low-pass filter at 1 kHz

- EQ filter at 1 kHz with a gain of 8 dB and a bandwidth of 500 Hz

The audio performance that was measured is shown in Table 7–1. The response shapes of the three test filters are shown in Figure 7–2.

| PARAMETER | FILTER                                                    | CONDITIONS                                  | MEASURED               |

|-----------|-----------------------------------------------------------|---------------------------------------------|------------------------|

|           | All-pass                                                  | Vol = 0, mixer –0 dB, 48-kHz f <sub>S</sub> | < -110 dB<br>< 0.0003% |

| THD+N     | 1-kHz second-order Butterworth high- and low-pass filters | Vol = 0, mixer –0 dB, 48-kHz f <sub>S</sub> | < -106 dB<br>< 0.0005% |

|           | 1-kHz EQ +8 dB, 500-Hz bandwidth                          | Vol = 0, mixer –8 dB, 48 kHz f <sub>S</sub> | < -108 dB<br>< 0.0004% |

| SNR       | All filters                                               |                                             | > 110 dB               |

| IM        | All filters                                               |                                             | < -98 dB<br>< 0.001%   |

| Table 7–1 | Audio | Filter | Performance |

|-----------|-------|--------|-------------|

|           | Audio | Inter  | renormance  |

Figure 7–2. Audio Performance Test Filters

# 8 Using the TAS3001 in a System

# 8.1 TAS3001 Applications

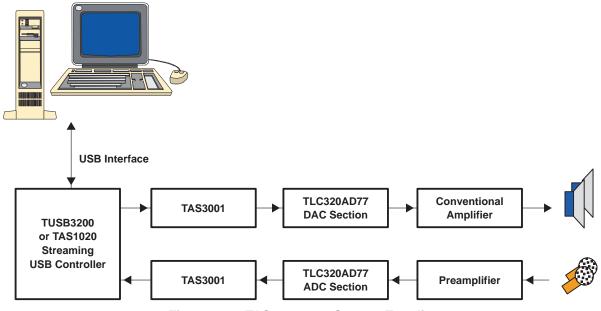

The TAS3001 can be used to perform a number of audio processing functions.

The TAS3001 can be used to perform parametric equalization to correct the frequency response of a pair of loudspeakers and microphones as shown in Figure 8–1. In this case, the TAS3001 is used to shape the frequency response of the transducers by applying filters to compensate for the response irregularities of each transducer (peaks and valleys of the microphone and loudspeaker response).

Figure 8–1. TAS3001 as a System Equalizer

The filters can be developed and evaluated using a personal computer, the TAS3001 EVM, a speaker analysis package, and the automatic loudspeaker equalization program. The next section demonstrates the use of the Texas Instruments automatic loudspeaker equalization program that automates many of the steps in developing filters for loudspeaker equalization.

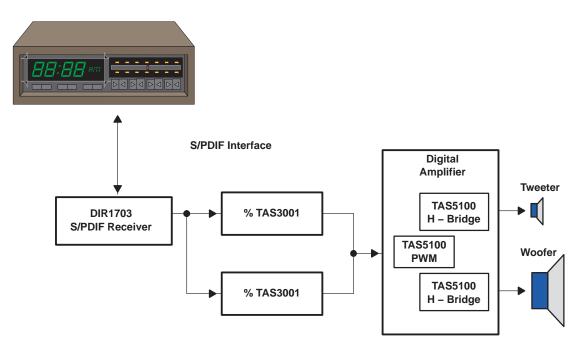

A second application of the TAS3001 is to perform both the crossover and frequency equalization of individual loudspeaker drivers in a two- or multi-way loudspeaker design as in Figure 8–2. In this case, the TAS3001 provides two functions: the crossover band-pass and band-limiting functions for each speaker and the compensation for the response irregularities of each loudspeaker driver.

Figure 8–2. TAS3001 as a Crossover and Equalizer

# 8.2 Measurement-Based Speaker Correction

Although loudspeakers ideally should be designed for a uniform sound pressure response as a function of frequency, cost and physical constraints usually result in speakers that are less than ideal. To correct large nonlinearities in the response or to shape the response to listener preferences, speaker equalization can be performed.

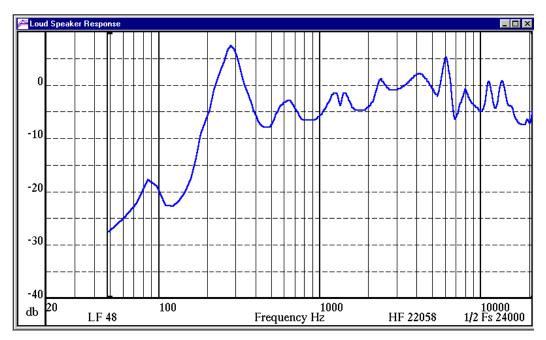

In the example speaker response shown in Figure 8–3, it is seen that the sound pressure level (y-axis) varies significantly as a function of frequency (x-axis). For speakers such as this typical loudspeaker, equalization can improve performance and enhance the listening experience.

Figure 8–3. Typical Small Loudspeaker Response

In addition to equalization of the frequency response, the TAS3001 can be used to notch out specific frequencies that excite mechanical resonances in the speaker. The removal of mechanical resonances improves the temporal response of the loudspeaker, so that it more accurately reproduces a recorded signal. For small and ported loudspeakers, a high-pass filter eliminates signal energy that is lower than the speaker can reproduce. This filtering improves the loudspeaker power handling and intelligibility by eliminating large cone excursions produced by signals that are below the loudspeaker resonant frequency.

The kinds of corrections being discussed here begin with a thorough understanding of the inherent operation of the particular loudspeaker. This information can best be obtained by means of a measurement such as that shown in Figure 8–3. The measurement information allows the equalization designer to find the resonances and other problems associated with the speaker and to correct them.

# 8.3 Sound-Based Speaker Correction

While a high-quality speaker measurement can be extremely valuable to the equalization designer, many good equalization designers also rely upon their own perception of the sound from the speaker. Based upon what they measure and hear, designers are able to design filters to achieve a specific frequency response and desired sonic character. Digital filters can be used to provide these corrections and shape the produced sound.

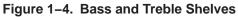

# 8.4 Loudspeaker Equalization Example

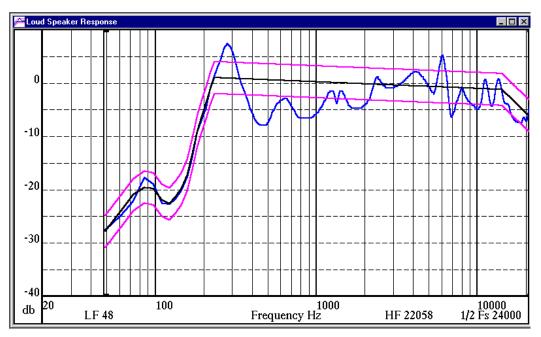

An example of loudspeaker equalization follows. In Figure 8–3, a loudspeaker has the frequency response shown. In Figure 8–5 the designer specifies the desired response that is the center of the three new lines. The lines above and below the center line are the + and – tolerances. The tolerances can be adjusted.

Figure 8–4. Preparation for Equalization

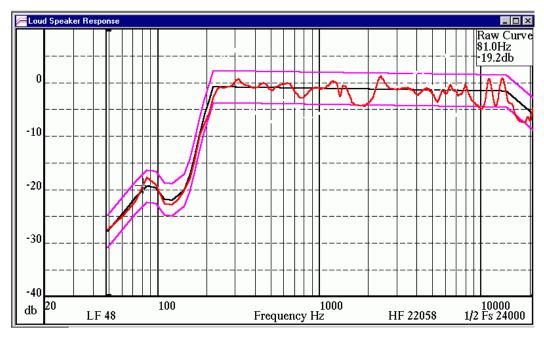

Figure 8–5 shows the corrected loudspeaker response that has been developed by the ALE program.

Figure 8–5. After Equalization

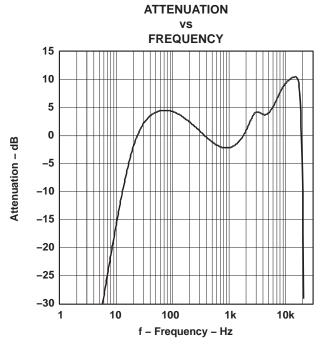

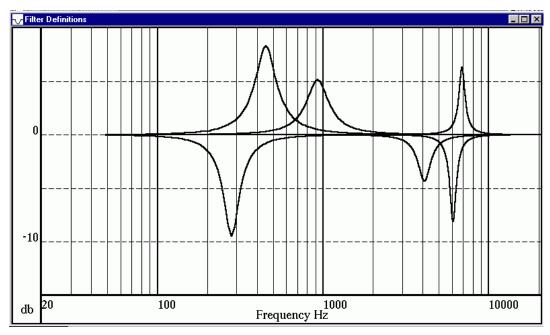

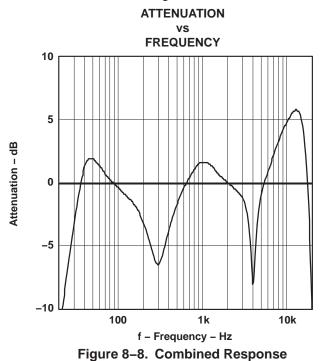

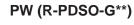

Figure 8–6 shows the filters that were used to equalize the loudspeaker response.

Figure 8–6. Equalization Filters

## 8.5 Speaker Correction and Equalization

Digital filters are able to provide a fairly broad range of filter types and responses.

The TAS3001 contains six programmable filters. The system designer has the choice of using one to all six of these filters. The filters can be used to equalize response peaks and dips from a desired response. They can also be used to shape the loudspeaker phase response. Because of their available precision and temperature insensitivity, not only can the filters be used to equalize the frequency and phase response of a loudspeaker closely, but they also can be used to remove resonances or other small deviations in the response of a loudspeaker surgically. This permits the system designer a greater degree of flexibility in the design of both the individual loudspeaker drivers and the cabinet. If additional filtering is needed, multiple TAS3001s can be cascaded.

This enables greater freedom in the design of acoustical systems. The TAS3001 permits additional flexibility in transducer design. Overall flatness of a transducer response is no longer an overriding concern with the low-cost/high-performance frequency correction of the TAS3001. The constraints on the transducer design can be relaxed so that they provide optimum performance after correction. This, in turn, allows the transducer and its equalization to be designed as a system, providing wide flexibility in the design and achieving outstanding sound presentation.

# 8.6 The TAS3001 Can Implement Nearly Any Second-Order IIR Filter

Filter designs can tax computational resources, so it is not uncommon to see simplified filter implementations that must limit either the number of or the nature of the filters that can be implemented. For example, a particular architecture might impose limits on the gains, Qs, and/or center frequencies that can be implemented. This, however, is not the case with the TAS3001. Its high-precision, patent-pending structure allows implementation of almost any second-order IIR filter. These are implemented in an almost limitless range of filter functions without fear of degradation due to limit cycles or increased system noise.

Additionally, higher order filters can be developed by factoring the desired filter into consecutive multiple second-order sections. Similarly, any filter that has been designed in analog can be converted and implemented as a digital filter.

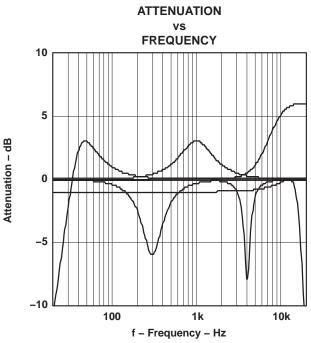

From left to right the filters that are shown in Figure 8–7 are:

- Variable Q high-pass filter with a Q = 1.3 to emphasize the bass and prevent distortion by cutting of frequencies below the cabinet resonance

- Equalization filters of various amplitudes, center frequencies, and bandwidths

- A treble shelf

- A Chebychev low-pass filter with a ripple of 1 dB to attenuate high frequencies

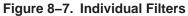

The combined response of these filters is shown in Figure 8–8.

8–6

# 8.7 Converting Analog Filters to Digital